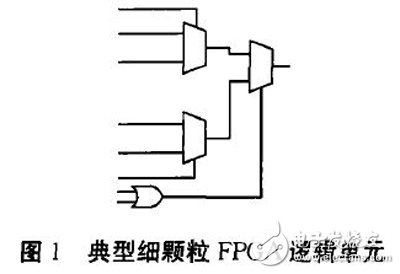

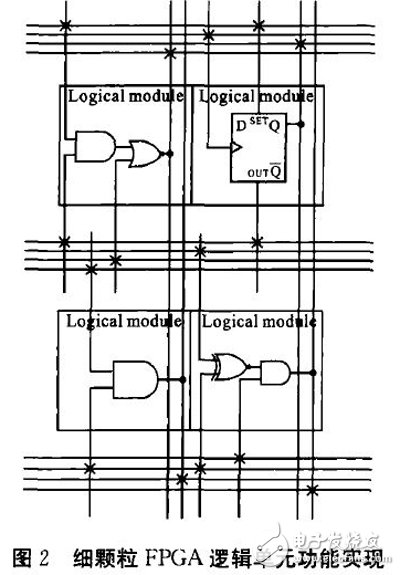

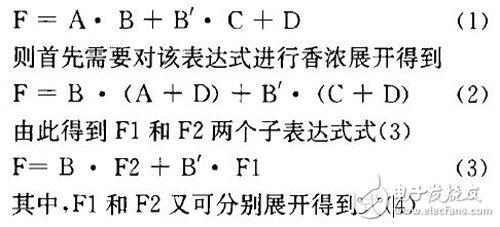

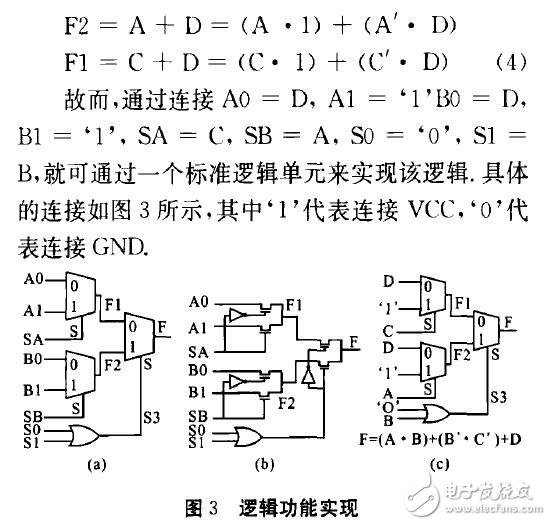

Abstract: Anti-fuse FPGAs are difficult to manufacture and are used in special applications. Therefore, there are few researches on their bitstream files. This paper first introduces the anti-fuse FPGA and FPGA CAD software flow, and then describes the specific structure of the anti-fuse FPGA. A specific example shows how to configure the anti-fuse FPGA, and then discusses the programming method of the anti-fuse FPGA, which leads to the format of the bit stream file and the programming information format of the anti-fuse unit. Finally, the anti-fuse FPGA bit is proposed. The stream file generation algorithm is implemented on the experimental platform. FPGA (Field Programmable Gate Array) is one of the most important three types of core digital devices in the current semiconductor market alongside CPU and DSP. Anti-fuse FPGA is the mainstream FPGA used in space field due to its high reliability and radiation resistance. . The CAD process of a typical FPGA consists of logic synthesis, process mapping and packaging, layout, routing, timing analysis, and bitstream generation. The logic synthesis is responsible for translating the circuit described in the hardware description language or schematic form into a basic gate table, and Perform process-independent logic optimization. The process map converts the process-independent gate-level netlist into the target cell's logical unit. The netlist layout tool determines the specific location of each logic cell required to implement the circuit function in the FPGA. According to the result of the layout, the input output pins of each logic unit are connected by appropriate wiring resources. The FPGA bit stream file (bit-stream) refers to the binary data set configured for the programmable logic device. This data set determines the specific function of the FPGA. The bit stream file specifically describes the information of the anti-fuse to be configured. This information can be used to program the FPGA to generate the target circuit. Since there is no specific data for reference, and the current FPGA architecture is characterized by diversity, the versatility of bitstream file design is not strong, so it can only be based on the basic principle of bitstream files. With the structure of the anti-fuse FPGA, the bit stream generation algorithm is designed for the anti-fuse FPGA according to the software engineering method. The configuration of the FPGA can be roughly divided into three parts: the logic unit configuration, the wiring switch configuration, and the input output unit configuration. For the fine particle anti-fuse FPGA, since the logic unit is customized, that is, it does not need to be configured, it implements different logic. The ability does not depend on the logical unit itself, but by selecting a different connection between its individual input pins and routing resources. Figure 1 shows a typical fine-grained FPGA logic unit. Since the selector can implement any logic property, multiple selectors can be combined to form a logic unit. The logic unit shown in Figure 2 can be used with routing resources. The roubles are arranged in combination to implement a large number of logic gates. The following describes an example of a specific configuration logic unit, if you need to implement the logic of (1) Similarly, for the I/() port, it can be determined by connecting the input, output pin and routing resources of each port to determine whether it is an input port or an output port. It can be seen that the fine particles are melted. The configuration of the silk FPGA is actually to configure the routing resources. Therefore, the generation of the bit stream configuration file is also greatly simplified. Only the anti-fuse information that needs to be configured inside the FPGA needs to be integrated to obtain the required bit stream file. Dust Explosion Proof Motor,Explosion Proof Induction Ac Motor,Special Explosion-Proof Motor,Dust Explosion Protection Motors Yizheng Beide Material Co., Ltd. , https://www.beidevendor.com